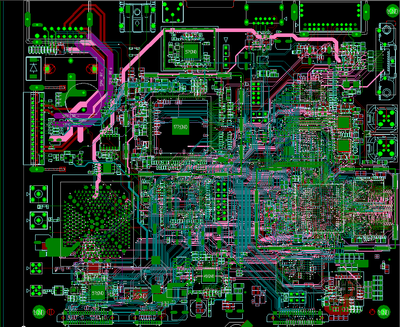

万龙精益PCB设计/PCB制板、PCBA智能制造/BOM采购的电子产业加速器服务平台

集成电路产业加速服务平台

实现硬科技从设计到交付全过程的一站式服务

万龙精益PCB设计/PCB制板、PCBA智能制造/BOM采购的电子产业加速器服务平台

集成电路产业加速服务平台

实现硬科技从设计到交付全过程的一站式服务

万龙精益PCB设计/PCB制板、PCBA智能制造/BOM采购的电子产业加速器服务平台

万龙精益PCB设计/PCB制板、PCBA智能制造/BOM采购的电子产业加速器服务平台

1、问:要提高抗干扰性,除了模拟地和数字地分开只在电源一点连接,加粗地线和电源线外,希望给一些好的意见和建议!

答:除了地要分开隔离外, 也要注意模拟电路部分的电源, 如果跟数字电路共享电源, 最好要加滤波线路。 另外, 数字信号和模拟信号不要有交错, 尤其不要跨过分割地的地方(moat)。

2、关于高速PCB设计中信号层空白区域敷铜接地问题

问:在高速PCB设计中,信号层的空白区域可以敷铜,那么多个信号层的敷铜是都接地好呢, 还是一半接地,一半接电源好呢?

答:一般在空白区域的敷铜绝大部分情况是接地。 只是在高速信号线旁敷铜时要注意敷铜与信号线的距离, 因为所敷的铜会降低一点走线的特性阻抗。 也要注意不要影响到它层的特 性阻抗, 例如在dual stripline的结构时。

3、高速信号线的匹配问题

问:在高速板(如p4的主板)layour,为什么要求高速信号线(如cpu数据,地址信号线)要匹配? 如果不匹配会带来什么隐患?其匹配的长度范围(既信号线的时滞差)是由什么因素决定的?

答:要求走线特性阻抗匹配的主要原因是要避免高速传输线效应(transmission line effect)所引起的反射(reflection)影响到信号完整性(signal integrity)和延迟时间(flight time)。也就是说如果不匹配,则信号会被反射影响其质量。所有走线的长度范围都是根据时序(timing)的要求所订出来的。影响信号延迟时间的因素很多,走线长度只是其一。P4要求某些信号线长度要在某个范围就是根据该信号所用的传输模式(common clock或source synchronous)下算得的timing margin,分配一部份给走线长度的允许误差。

4、问: 在高密度印制板上通过软件自动产生测试点一般情况下能满足大批量生产的测试要求吗?添加测试点会不会影响高速信号的质量?

答:一般软件自动产生测试点是否满足测试需求必须看对加测试点的规范是否符合测试机具的要求。另外,如果走线太密且加测试点的规范比较严,则有可能没办法自动对每段线都加上测试点,当然,需要手动补齐所要测试的地方。至于会不会影响信号质量就要看加测试点的方式和信号到底多快而定。基本上外加的测试点(不用线上既有的穿孔(via or DIP pin)当测试点)可能加在线上或是从线上拉一小段线出来。前者相当于是加上一个很小的电容在线上,后者则是多了一段分支。这两个情况都会对高速信号多多少少会有点影响,影响的程度就跟信号的频率速度和信号缘变化率(edge rate)有关。影响大小可透过仿真得知。原则上测试点越小越好(当然还要满足测试机具的要求)分支越短越好。

万龙精益,为广大客户提供从硬件设计、智能制造到智能产品的一站式服务,让您节省时间精力、生产成本和致力于新产品的研发和销售。并拥有研发设计能力和产品制造能力,致力于快速将您的需求变成智能硬件。

万龙精益推荐的主要服务有:

设计:PCB设计、PCB layout、PCB线路板设计、PCB原理图设计、PCB抄板、工业设计、外观结构设计、ODM设计等设计服务 ;

加工:PCB板打样制作、SMT贴片加工、电路板焊接加工、PCBA加工、PCBA代工代料、绕制线圈、OEM加工等加工服务;

相关文章: