在上一篇文章PCB设计技巧中:PCB设计布线技巧问答中介绍了关于如何计算PCB布线调整、关于关于高速数字PCB、以及电路板DEBUG等等,下面继续更新。

1.现在常用的电子PCB设计软件如何满足电路抗干扰的要求?

1.现在常用的电子PCB设计软件如何满足电路抗干扰的要求?

问: 现在有哪些PCB设计软件,如何用PROTEL99合理的设计符合自己要求的PCB.比如如何满足高频电路的要求,如何考虑电路满足抗干扰的要求?

答:我没有使用Protel的经验,以下仅就设计原理来讨论。

高频数字电路主要是考虑传输线效应对信号质量与时序(timing)的影响。如特性阻抗的连续与匹配,端接方式的选择,拓朴(topology)方式的选择,走线的长度与间距,时钟(或strobe)信号skew的控制等。

如果器件已经固定,一般抗干扰的方式是拉大间距或加ground guard traces

2.关于lvds信号的布线

问: 对于lvds低压差分信号,原则上是布线等长、平行,但实际上较难实现,是否能提供一些经验?

答 差分信号布线时要求等长且平行的原因有下列几点:

1.平行的目的是要确保差分阻抗的完整性。平行间距不同的地方就等于是差分阻抗不连续。

2. 等长的目的是想要确保时序(timing)的准确与对称性。因为差分信号的时序跟这两个信号交叉点(或相对电压差值)有关,如果不等长,则此交叉点不会出现在信号振幅(swing amplitude)的中间,也会造成相邻两个时间间隔(time interval)不对称,增加时序控制的难度。

3.不等长也会增加共模(common mode)信号的成分,影响信号完整性(signal integrity)。

3. 问:在电路板尺寸固定的情况下,如果设计中需要容纳更多的功能,就往往需要提高PCB的走线密度,但是这样有可能导致走线的相互干扰增强,同时走线过细也使阻抗无法降低,介绍在高速(>100MHz)高密度PCB设计中的技巧?

答:在设计高速高密度PCB时,串扰(crosstalk interference)确实是要特别注意的,因为它对时序(timing)与信号完整性(signal integrity)有很大的影响。以下提供几个注意的地方:

1.控制走线特性阻抗的连续与匹配。

2.走线间距的大小。一般常看到的间距为两倍线宽。可以透过仿真来知道走线间距对时序及信号完整性的影响,找出可容忍的最小间距。不同芯片信号的结果可能不同。

3.选择适当的端接方式。

4.避免上下相邻两层的走线方向相同,甚至有走线正好上下重迭在一起,因为这种串扰比同层相邻走线的情形还大。

5.利用盲埋孔(blind/buried via)来增加走线面积。但是PCB板的制作成本会增加。

在实际执行时确实很难达到完全平行与等长,不过还是要尽量做到。除此以外,可以预留差分端接和共模端接,以缓和对时序与信号完整性的影响。

万龙精益,为广大客户提供从硬件设计、智能制造到智能产品的一站式服务,让您节省时间精力、生产成本和致力于新产品的研发和销售。并拥有研发设计能力和产品制造能力,致力于快速将您的需求变成智能硬件。

万龙精益推荐的主要服务有:

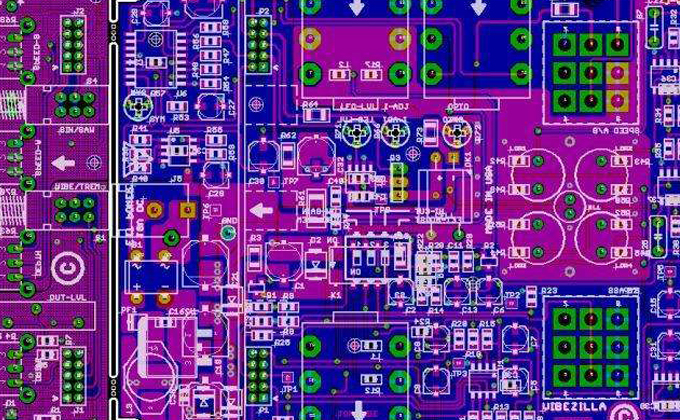

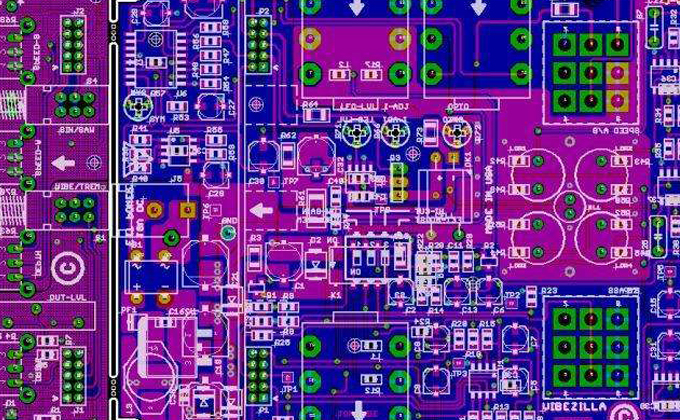

设计:PCB设计、PCB layout、PCB线路板设计、PCB原理图设计、PCB抄板、工业设计、外观结构设计、ODM设计等设计服务 ;

加工:PCB板打样制作、SMT贴片加工、电路板焊接加工、PCBA加工、PCBA代工代料、绕制线圈、OEM加工等加工服务;

产品:自主研发的电子产品、元器件代购.......了解更多请联系万龙精益,更多产品请访问 万龙精益淘宝店铺。

万龙精益PCB设计/PCB制板、PCBA智能制造/BOM采购的电子产业加速器服务平台

万龙精益PCB设计/PCB制板、PCBA智能制造/BOM采购的电子产业加速器服务平台