��������PCB���/PCB�ư塢PCBA��������/BOM�ɹ��ĵ��Ӳ�ҵ����������ƽ̨

���ɵ�·��ҵ���ٷ���ƽ̨

ʵ��Ӳ�Ƽ�����Ƶ�����ȫ���̵�һվʽ����

��������PCB���/PCB�ư塢PCBA��������/BOM�ɹ��ĵ��Ӳ�ҵ����������ƽ̨

���ɵ�·��ҵ���ٷ���ƽ̨

ʵ��Ӳ�Ƽ�����Ƶ�����ȫ���̵�һվʽ����

��������PCB���/PCB�ư塢PCBA��������/BOM�ɹ��ĵ��Ӳ�ҵ����������ƽ̨

��������PCB���/PCB�ư塢PCBA��������/BOM�ɹ��ĵ��Ӳ�ҵ����������ƽ̨

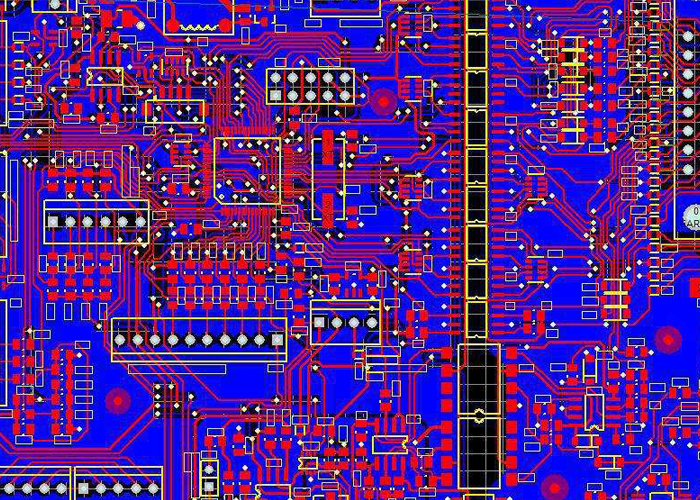

1. PCB�IJ��ߵ���

����һ������:����������IJ�����,��������������ʱ��һ�����õ��ֹ�����,���ڸ��PCB����Ҫ�������ܶȽϴ����Ƭ��װоƬ,���Ҵ�����(ABUS,DBUS,CBUS��),����Ƶ�ʽϸ�,������Ҫ�����ܶ�.��Ȼ�ľ��Ǻ��ܵ��ź����Ȳ���С��Χ����İ����ϡ�

�о�������ʱ��϶���ǵ�����Щ�ܶȴ���ź���, һ�ǵ�����ľ���,ʹ֮�����ܵľ��ȡ���Ϊ�ڲ��ߵĹ�����,һ��Ķ�ʱ��ʱ��Ҫ���ߡ�ÿ��һ�ζ�Ҫ���¾���ÿһ���Ѳ��õ��ߵļ�ࡣԽ�Dz�������������Խ�Ƕࡣ���ǵ����ߵĿ���,ʹ֮��һ�������о����ܵ��������ӵ��ߡ�һ��һ�������кܶ�����,һ�������һ��,�ֹ�����ֻ��һ��һ�εص���,��������Ҳ��ʱ�䡣

����ڲ��ߵĹ�����,�ܰ��ҵ�˼·�ȴִֵ��ֹ�����,�����Ժ�, �����ܴ���������������Զ��ص��������Ǽ����Ѳ��꣬��Ҫ���ߣ�Ҳ�Ǵִֵظ�һ�£�Ȼ��������������������������Ҿ�����Ҫ����Ԫ���ķ�װ��Ҳ����˵��Ƭ���߶���Ҫ�����������������ɡ�������Ҫ�����.���õ���Protel98����֪�������������Զ����ȵ���Ԫ����װ�ľ���������Զ������߾���߿������������е�һЩ�����һ�������,����������ʲô�취,�ڴ����һ�¡�

��:�߿����߾���Ӱ�������ܶ�����������Ҫ�����ء�һ������ƹ���Ƶ�ʽϸߵİ���ʱ������֮ǰ��Ҫ�Ⱦ������ߵ������迹����PCB����̶�������£������迹����������ϵ��߿������߾���ʹ���(Crosstalk) ��С�о��ԵĹ�ϵ����С���Խ��ܵ��߾�����ڴ��Ŷ��ź�ʱ���ӳ����ź������Ե�Ӱ���Ƿ��ܽ��ܡ�����С�߾���ɷ���������Ԥ����(pre- simulation)�õ���Ҳ����˵���ڲ���֮ǰ����Ҫ���߿�����С�߾�Ӧ���Ѿ��������ˣ����Ҳ��������������Ϊ��Ӱ�������迹�ʹ��š���Ҳ��Ϊʲ�۴ֵ�EDA�������������Զ��������ʱ����ȥ���߿�����С�߾ࡣ������߿�����С�߾��Ѿ��趨���ڲ������������ߵ����ķ������Ϳ������������������ǿ��������������Աι�˾Expedition����Ȥ�Կ������ǵ��������棬

2. ���ڸ�������PCB

�����ʵ�ѡ��PCB����ǽӵصĵ��ԭ����ʲô?���⣬һ��PCB LAYOUT����ʦ���Ǹ���DESIGN GUIDE/LAYOUT GUIDELINE���������˽�һ���ƶ�GUIDE����Ӳ��/ϵͳ����ʦ����������PCB����ʦ?˭Ӧ�ö弶ϵͳ�����ܸ���Ҫ���Σ�

��: ����ǽӵص�ѡ���ԭ��������chassis ground�ṩ���迹��·������������(returning current)�����ƴ˻���������·�������磬ͨ���ڸ�Ƶ������ʱ�Ӳ������������Խ�̶��õ���˿��PCB�ĵز���chassis ground�����ӣ��Ծ�����С����������·�����Ҳ�ͼ��ٵ�ŷ��䡣˭Ӧ�ø����ƶ�guideline����ÿ����˾�в�ͬ��������в�ͬ���š�Guideline���ƶ����������ϵͳ��оƬ����·����ԭ���г�ֵ��˽⣬�����ƶ������ϵ����淶�ҿ�ʵ�ֵ�guideline�����ԣ����Ҹ��˵Ĺ۵㣬Ӳ��ϵͳ����ʦ�ƺ����ʺ������ɫ����Ȼ������PCB����ʦ�����ṩ��ʵ��ʵ��ʱ�ľ��飬ʹ����guideline����ʵ�ֵĸ��á�

3.��·��DEBUGӦ���Ǽ����������֡�

�ʣ����ʰ�����ƺã�����������DEBUGӦ���Ǽ����������֡�

�𣺾����ֵ�·���ԣ�����������ȷ���������飺

1.ȷ�����е�Դֵ�Ĵ�С���ﵽ������衣��Щ���ص�Դ��ϵͳ���ܻ�Ҫ��ijЩ��Դ֮��������˳���������ij�ֹ淶��

2.ȷ������ʱ���ź�Ƶ�ʶ������������źű�Ե��û�зǵ���(non-monotonic)�����⡣

3.ȷ��reset�ź��Ƿ�ﵽ�淶Ҫ��

��Щ�������Ļ���оƬӦ��Ҫ������һ������(cycle)���źš�����������ϵͳ����ԭ����bus protocol��debug��

����������Ϊ���ͻ��ṩ��Ӳ��������������������ܲ�Ʒ��һվʽ����������ʡʱ�侫���������ɱ����������²�Ʒ���з������ۡ���ӵ���з���������Ͳ�Ʒ���������������ڿ��ٽ���������������Ӳ����

���������Ƽ�����Ҫ�����У�

��ƣ�PCB�����PCB layout��PCB��·�������PCBԭ��ͼ�����PCB��������ҵ�������۽ṹ�����ODM��Ƶ���Ʒ��� ;

�ӹ���PCB������������SMT��Ƭ�ӹ�����·�庸���ӹ���PCBA�ӹ���PCBA����������������Ȧ��OEM�ӹ��ȼӹ�����;

��Ʒ�������з��ĵ��Ӳ�Ʒ��Ԫ��������.......�˽��������ϵ���������������Ʒ����� ���������Ա�������

������£�

����Ƽ���